どうも、ヴィンテージ水晶発振子を使った時計の続きです。

今回は、地味だけど実は重要な、電源とリセット回路に触れておきます。

目次

- 概要と機能・動作

- 材料

- クロック回路

- 時計(時刻のカウント)

- 時刻合わせ

- VFD点灯制御

- 電源、リセット ← 今回はココ!!

- 実装(はんだ付け、筐体)

- 完成までのストーリー

この回路の役割

電源はその名の通り、回路全体に適切な電力を供給するものです。

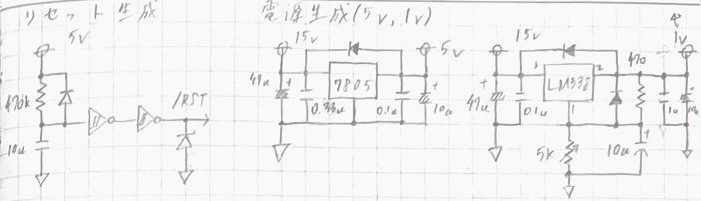

リセット回路は起動時から一定の間、ロジックICのリセットをかけるもので、水晶発振子のクロックと動作の足並みをそろえるために使います。

電源回路

実はロジックIC、VFD管(グリッド、アノード)とフィラメント用に、それぞれ別の電源を用意しています。供給する電圧は以下の通り。

- ロジックIC:5V

- VFD管(グリッド、アノード):12V

- VFD管フィラメント:1V x 6(本数)

今回のVFD管(IV-6)は、データシートによるとグリッド・アノードが25V、フィラメントが0.85~1.15V必要になるようです。ただ、12Vでも(少し暗いですが)点灯するので、この回路では12Vにしました。

それに伴い、大本の電源は12V出力のACアダプタにしており、これをVFD管へ供給、および他の電圧への変換元として使っています。もう少し明るさが欲しい場合は15~24Vに上げて、以下のフィラメント用電源回路を適切に設計します。

ロジックICへの電源は3.3Vまたは5Vが一般的ですが、今回は三端子レギュレータのNJM7805(出力5V, 1.5A)が余っていたので5Vにしました。中には低電圧のもありますが、なるべく駆動電圧は統一して、どうしても混ぜる場合は電圧トレラント(5Vトレラント)かレベル変換ICを使うようにしましょう。

また、今は消費電流が小さいCMOSが主流なので電力不足に陥ることは早々ありませんが、数百個単位で増えてきたりTTLなどに代えると電力オーバーになる可能性もなくはないので一応注意(この回路でTTLにしても問題ないとは思いますが)。

一方、VFD管フィラメントの電源(1V x 6)は可変型レギュレータであるLM338を使用しました。

このレギュレータはGNDの代わりにADJピンを持ち、出力ピンとADJの間に固定抵抗、ADJとGNDの間に可変抵抗を入れることで、抵抗比から電圧を調整することが可能です(Vout-ADJ-GNDピン間で分圧回路を作るイメージ)。フィラメントは1本につき約1Vで直列につなげるので、本数と同じ数の電圧をかければOK。

リセット回路

ラッチを含むデジタル回路は初期状態が不定なため、前も参考にしたこのサイトに従い、電源ONの直後に状態を初期化する回路を設けました。

ただ、ICの初期化としての役割もありますが、同時に水晶発振子が安定するまでのタイマーとしての意味合いもあります。

構成は抵抗とコンデンサ(+放電用ダイオード)、2個のシュミットトリガインバータからなる遅延回路です。今回の水晶発振子は安定するまで約2~3秒くらいかかるため、時定数が5秒前後になるよう、抵抗値を470kΩ、コンデンサの容量を10uFとしました。

メイキング

電源回路を制作している3倍速動画です。